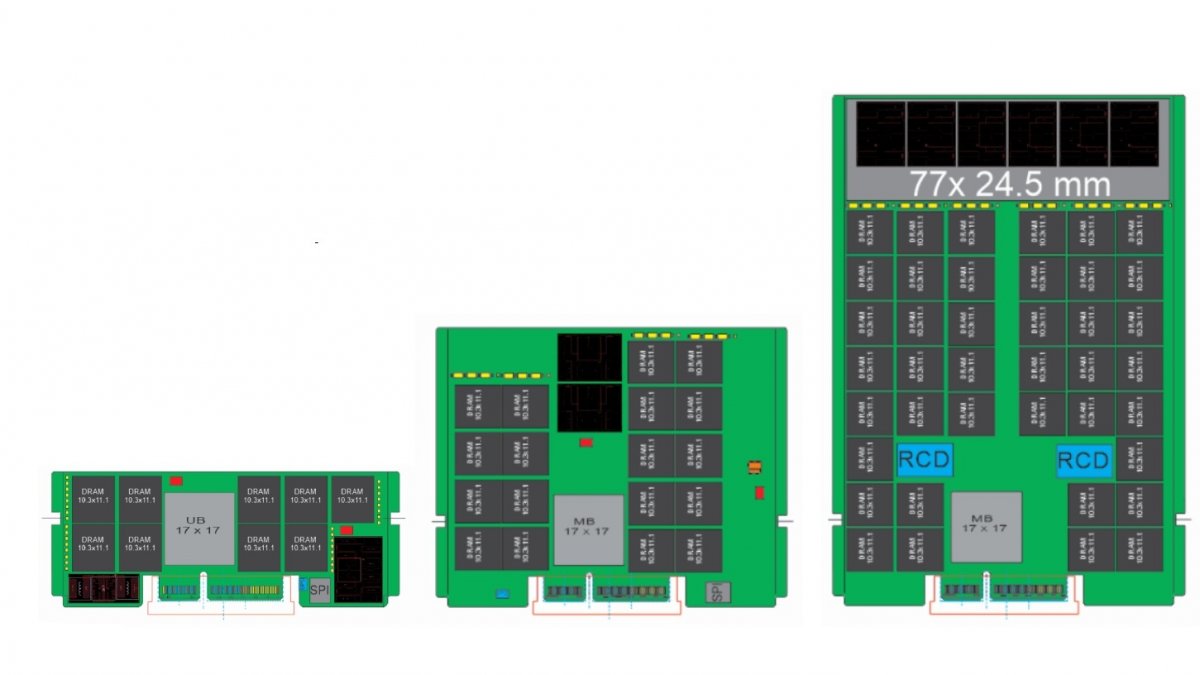

OpenCAPI Memory Interface Signal Integrity Study for High-Speed DDR5 Differential DIMM Channel with Standard Loss FR-4 Material

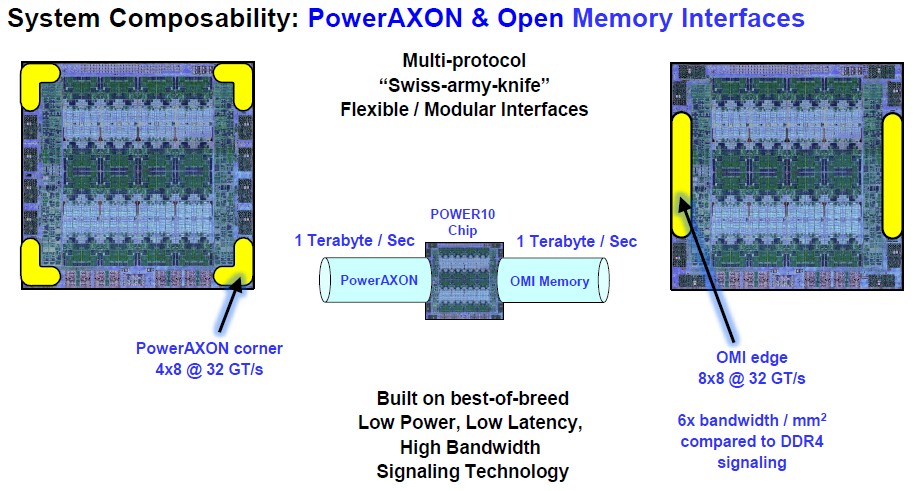

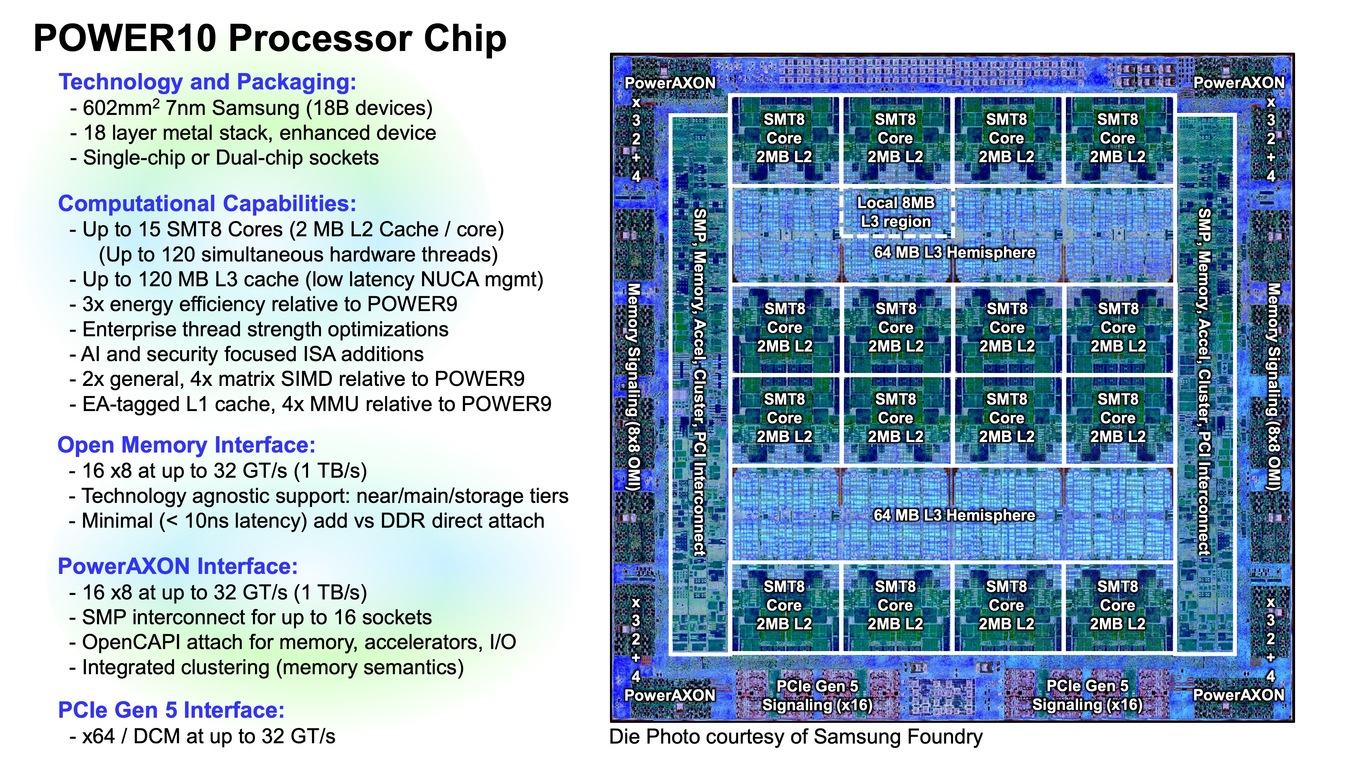

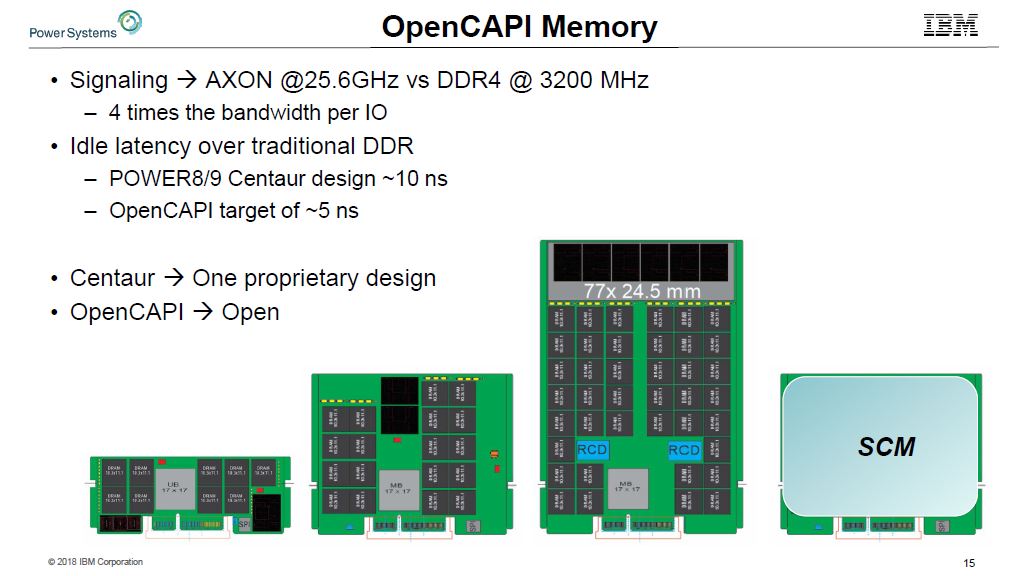

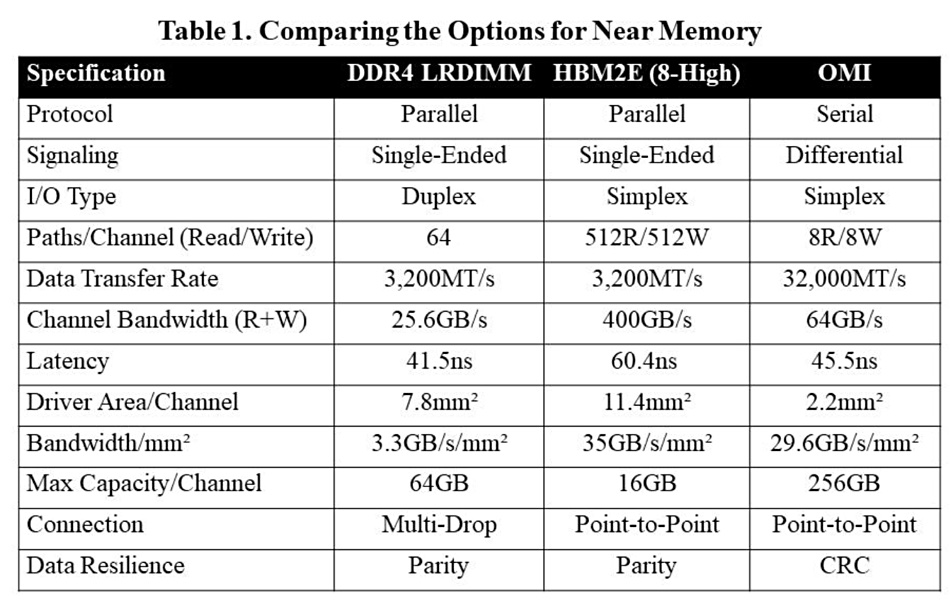

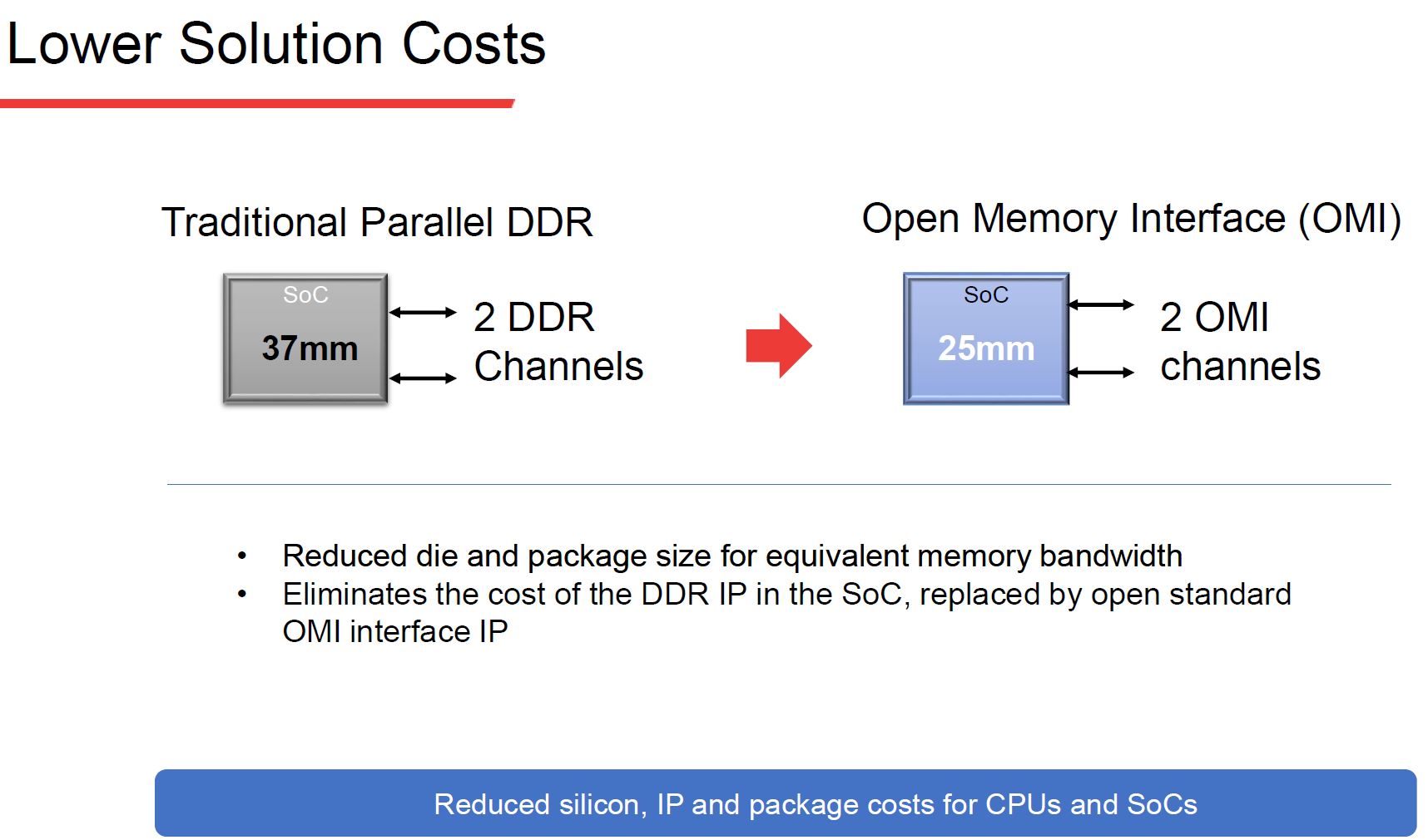

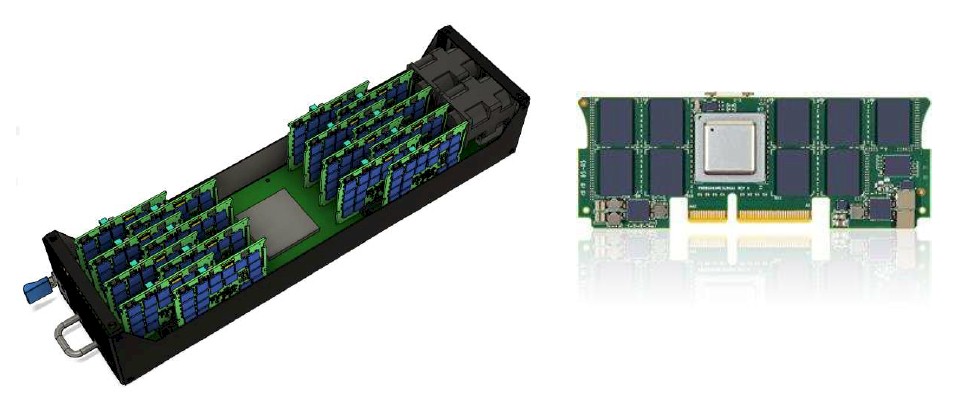

OGAWA, Tadashi on X: "=> Microchip: Serial Memory Controller for High-performance Data Center Computing, Aug 5 2019 https://t.co/MkqlfbrAv8 SMC 1000 8x25G https://t.co/ZmjP5LOr5V https://t.co/ynUcZBeZel Open Memory Interface 8x 25 Gbps OpenCAPI ...