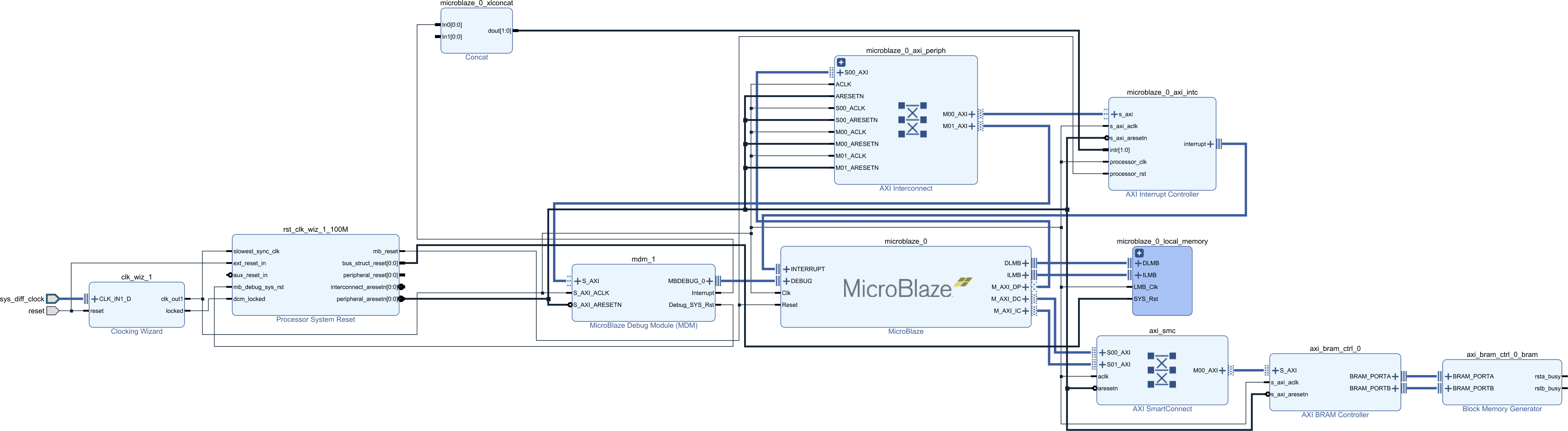

BD 41-2388] ROM instance </axi_bram_ctrl_0_bram> was detected as Microblaze </microblaze_0> Local Memory. ROM instances cannot be initialized with ELF data. Please change the configuration of the me

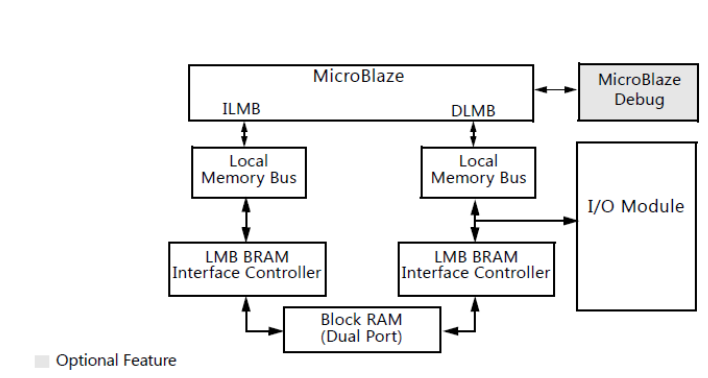

Multiprocessor based on shared memory/bus Fig 2 presents the second... | Download Scientific Diagram